Active Theses

Extending the RIPES Processor Simulator

Type:

Bachelor Thesis

Student:

Nico Schubert

Summary:

The goal of this thesis is to extend the RIPES simulator to support additional CPU models that are relevant for our lecture on computer architecture. Specifically, the following extensions should be implemented:

- Multicycle CPU as introduced in the lecture, with distinct stages for instruction fetch, decode, execute, memory access, and write-back.

- Pipelined CPU without support for reading and writing the register file in the same clock cycle.

- VLIW Pipeline (Static Dual-Issue) architecture, where two instructions can be issued in parallel under specific conditions. Instruction scheduling is assumed to be static and done at compile-time.

Additional extensions or models that align with the lecture content (to be discussed).

The requirements are a good understanding of computer architecture concepts (ideally through successful participation in the corresponding lecture), experience with C++ and Qt (RIPES is written in C++ with a Qt GUI) and the ability to work independently and structure a larger software project.

Supervisors:

RoRiV - a Real-Time Operating System on RISC-V CPUs

Type:

Bachelor Thesis

Student:

Andreas Theiner

Summary:

RoRiV -- The objective of this thesis is to port the real-time operating system (RTOS) RODOS [1] to RISC-V CPUs. RISC-V is an open-source instruction set architecture (ISA) that not only supports open software but also enables open hardware design. As part of this thesis, the feasibility of running RODOS on the BeagleV board will be explored. Additionally, it will be evaluated whether the OS can operate on JMU's custom-built TinyRV CPU, which is manufactured using a 130nm process [2]. The project will involve performance evaluation and optimization for real-time tasks on these platforms, offering a hands-on opportunity to work at the intersection of hardware and software in embedded systems.

Supervisors:

Prof. Sergio Montenegro, Prof. Andreas Nüchter and Prof. Matthias Jung

Links:

Development of APRS TX/RX iGate

Type:

Bachelor Thesis

Student:

Tilman Jackel

Summary:

Automatic Packet Reporting System (APRS) is an amateur radio-based system for real time digital communications of information of immediate value in the local area. Data can include object Global Positioning System (GPS) coordinates, weather station telemetry, text messages, announcements, queries, and other telemetry. APRS data can be displayed on a map, which can show stations, objects, tracks of moving objects, weather stations, search and rescue data, and direction finding data [2]. The objective of this project is to develop an APRS RX/TX iGate, on a custom designed PCB.

Supervisors:

Prof. Matthias Jung and Prof. Hakan Kayal

Links:

On the Application of Compilers to Custom RISC-V ISAs

Type:

Bachelor Thesis

Student:

Gabriel Rittershofer

Summary:

The objective of this thesis is the development of a flexible compiler capable of compiling an application to a tailored RISC-V architecture that includes only a subset of RISC-V instructions. This is particularly useful for small cores, such as those in accelerators, or small execution machines used in Processing in Memory applications. After developing the compiler, an analysis to examine the trade-off between the required chip area and the number of instructions, i.e., performance for several benchmark is conducted

Supervisor:

Development of a Hardware Accelerator

Type:

Master Project

Student:

Sebastian Gumbmann

Summary:

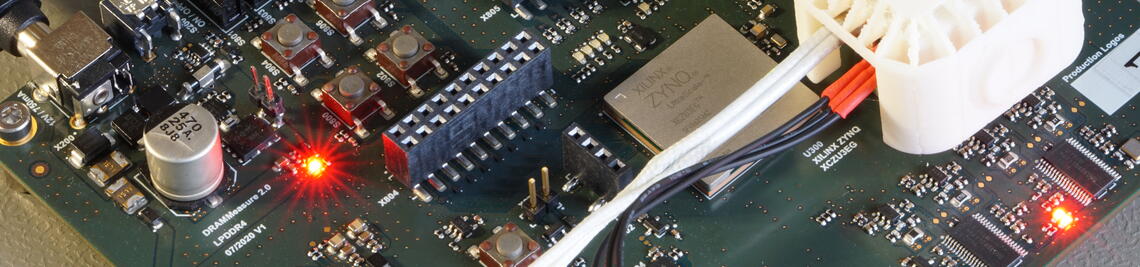

The objective of this project is to develop a hardware accelerator to solve a mathematical optimization problem. For the problem presented in [1] there exists a customized solver, based on C++/MPI, which can be executed on large computing clusters. The algorithm is based on an branch and bound algorithm. In each node some simple calculations have to be performed, which could also be accellerated on an FPGA.

Supervisors:

Links: