Publications

2026[ to top ]

-

A Formal Description of Communication Protocols Using Petri-Nets. . In 29th Workshop on Methods and Description Languages for Modelling and Verification of Circuits and Systems (MBMV). 2026.

- [ BibTeX ]

-

ARCADES: A RISC-V-Coupled Accelerator for Discrete Event Simulation. . In Proceedings of the 18th Workshop on Rapid Simulation and Performance Evaluation: Methods and Tools, of RAPIDO ’26. 2026.

- [ BibTeX ]

-

Autoformalizing Memory Device Specifications with Agents. . In VerifAI-2: The Second Workshop on AI Verification in the Wild @ ICLR’26. 2026.

- [ BibTeX ]

-

Accelerating Accurate DRAM Simulation Using Dynamic Binary Instrumentation For Online Trace Generation. . In 29th Workshop on Methods and Description Languages for Modelling and Verification of Circuits and Systems (MBMV). 2026.

- [ BibTeX ]

-

Open-Source-Chip-Design - A new Playground for Ham Radio. . 2026.

- [ BibTeX ]

2025[ to top ]

-

A Mathematical Model for XOR-Based Application Specific DRAM Address Mapping Schemes. . In Proceedings of the 11th International Symposium on Memory Systems (MEMSYS), Vol. 11. 2025.

- [ BibTeX ]

-

Performance and Power Analysis of LPDDR6. . In Proceedings of the 1st IEEE Cross-disciplinary Conference on Memory-Centric Computing (CCMCC), Vol. 1. 2025.

- [ BibTeX ]

-

Architecture, Simulation and Software Stack to Support Post-CMOS Accelerators: The ARCHYTAS Project. . In Proceedings of the 2025 IEEE Computer Society Annual Symposium on VLSI (ISVLSI). IEEE, 2025.

-

CHaOS: A Persistent Lightweight Cache Hybridization-aware OS. . In Architecture of Computing Systems, Vol. 38, pp. 63–78. Springer Nature Switzerland, 2025.

-

Exploiting LPDDR6 Metadata to Cache Byte-Addressable Non-Volatile Main Memories. . In Proceedings of the 1st IEEE Cross-disciplinary Conference on Memory-Centric Computing (CCMCC), Vol. 1. 2025.

-

Neuromorphe Systeme für energieeffizientes Rechnen. . In ATZelektronik, 20, pp. 16–21. 2025.

-

DRAMPower 5: An Open-Source Power Simulator for Current Generation DRAM Standards. . In Proceedings of the 17th Workshop on Rapid Simulation and Performance Evaluation: Methods and Tools, of RAPIDO ’25, pp. 8–16. ACM, Barcelona, Spain, 2025.

-

Ausbildung Mit 50Ohm.de. . In Amateurfunk-Tagung München. München, 2025.

- [ BibTeX ]

-

DRAMPyML: A Formal Description of DRAM Protocols with Timed Petri Nets. . In Design and Verification Conference and Exhibition (DVCON) Europe 2025. 2025.

-

Split’n’Cover: ISO 26262 Hardware Safety Analysis with SystemC. . In International Journal of Parallel Programming, 53(3). 2025.

-

PIMSys: A Virtual Prototype for Processing in Memory. . In 21st International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES25). Academia Press, Ghent, Belgium, 2025.

- [ BibTeX ]

-

Self-powered Embedded Systems: The Role of Non-volatile Memory Technology in IoT Devices. . In Go Where the Bugs Are: Essays Dedicated to Wolfgang Reif on the Occasion of His 65th Birthday, G. Ernst, M. Güdemann, A. Knapp, F. Nafz, F. Ortmeier, H. Ponsar, G. Schellhorn, A. Schiendorfer (eds.), pp. 155–177. Springer Nature Switzerland, Cham, 2025.

-

Modeling and Simulating Emerging Memory Technologies: A Tutorial. . 2025.

-

Towards the Utilization of Lensless Camera Sensors for Star Tracking Systems in Femto-satellites. . In 2025 IEEE CHILEAN Conference on Electrical, Electronics Engineering, Information and Communication Technologies (CHILECON). 2025.

- [ BibTeX ]

2024[ to top ]

-

QCEDA: Using Quantum Computers for EDA. . In International Conference on Embedded Computer Systems Architectures Modeling and Simulation (SAMOS). Springer, 2024.

-

The New Costs of Physical Memory Fragmentation. . In Proceedings of the 2nd Workshop on Disruptive Memory Systems, of DIMES ’24, pp. 33–40. Association for Computing Machinery, Austin, TX, USA, 2024.

-

How Far Is the Nanocellulose Chip and Its Production in Reach? A Literature Survey. . In Nanomaterials, 14(18). 2024.

-

Novel System Simulation Framework for HBM2 FPGA Platforms. . Springer, 2024.

- [ BibTeX ]

-

Hybrid Cache Design Under Varying Power Supply Stability - A Comparative Study. . In MEMSYS ’24: Proceedings of the International Symposium on Memory Systems, pp. 257–269. 2024.

-

DARC- Amateurfunklehrgang Klasse N. . First , M. Jung; B. Swierczek (eds.). DARC Verlag, 2024.

-

Challenges for Quantum Software Engineering: An Industrial Application Scenario Perspective. . In Quantum Software: Aspects of Theory and System Design, I. Exman, R. Pérez-Castillo, M. Piattini, M. Felderer (eds.), pp. 311–335. Springer Nature Switzerland, Cham, 2024.

-

To Keep or Not to Keep - The Volatility of Replacement Policy Metadata in Hybrid Caches. . In Proceedings of the 2nd Workshop on Disruptive Memory Systems, pp. 17–24. 2024.

-

PIMSys: A Virtual Prototype for Processing in Memory. . In Proceedings of the International Symposium on Memory Systems, of MEMSYS ’24, pp. 26–33. Association for Computing Machinery, New York, NY, USA, 2024.

2023[ to top ]

-

Neues Ausbildungsmaterial für alle Klassen. . In Amateurfunk-Tagung München. DARC e.V., Distrikt Oberbayern, 2023.

- [ BibTeX ]

-

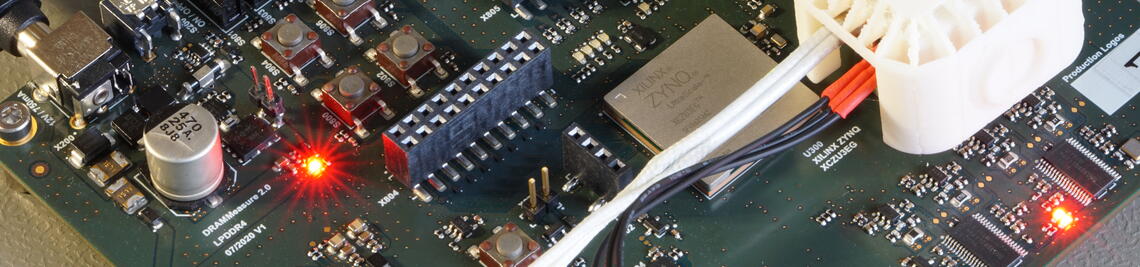

A Precise Measurement Platform for LPDDR4 Memories. . In ACM/IEEE International Symposium on Memory Systems (MEMSYS 2023). 2023.

- [ BibTeX ]

-

Automatic DRAM Subsystem Configuration with irace. . In Rapid Simulation and Performance Evaluation: Methods and Tools (RAPIDO). International Conference on High-Performance and Embedded Architectures and Compilers 2020 (HiPEAC), Workshop on, 2023.

- [ BibTeX ]

2022[ to top ]

-

Split’n’Cover: ISO26262 Hardware Safety Analysis with SystemC. . In Springer LNCS International Conference on Embedded Computer Systems Architectures Modeling and Simulation (SAMOS). 2022.

-

Unveiling the Real Performance of LPDDR5 Memories. . In ACM/IEEE International Symposium on Memory Systems (MEMSYS 2022). 2022.

-

DRAMSys4.0: An Open-Source Simulation Framework for In-Depth DRAM Analyses. . In Springer, International Journal of Parallel Programming (IJPP). 2022.

-

A Framework for Formal Verification of DRAM Controllers. . In ACM/IEEE International Symposium on Memory Systems (MEMSYS 2022). 2022.

-

A Weighted Current Summation based Mixed Signal DRAM-PIM Architecture for Deep Neural Network Inference. . In Journal on Emerging and Selected Topics in Circuits and Systems (JETCAS). 2022.

-

Amateurfunkprüfung: Zwischenstand neuer Fragenkatalog. . In Weinheimer UKW-Tagung. 2022.

2021[ to top ]

-

Online Working Set Change Detection with Constant Complexity. . In ACM/IEEE International Symposium on Memory Systems (MEMSYS 2021). 2021.

-

The Dynamic Random Access Memory Challenge in Embedded Computing Systems (Book Chapter in: A Journey of Embedded and Cyber-Physical Systems: Essays Dedicated to Peter Marwedel on the Occasion of His 70th {B}irthday). . Springer International Publishing, 2021.

-

SEC-Learn: Sensor Edge Cloud for Federated Learning. . In Embedded Computer Systems: Architectures, Modeling and Simulation (SAMOS XXI). 2021.

-

A Novel DRAM-Based Process-in-Memory Architecture and its Implementation for CNNs. . In 26th Asia and South Pacific Design Automation Conference (ASP-DAC 2021). 2021.

-

A Novel DRAM Architecture for Improved Bandwidth Utilization and Latency Reduction Using Dual-Page Operation. . In IEEE Transactions on Circuits and Systems II: Express Briefs. 2021.

-

Exploration of DDR5 with the Open Source Simulator DRAMSys. . In IEEE/VDE Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen MBMV. 2021.

-

An LPDDR4 Safety Model for Automotive Applications. . In ACM/IEEE International Symposium on Memory Systems (MEMSYS 2021). 2021.

2020[ to top ]

-

eBrainII: a 3 kW Realtime Custom 3D DRAM Integrated ASIC Implementation of a Biologically Plausible Model of a Human Scale Cortex. . In Journal of Signal Processing Systems. 2020.

-

A Low Power In-DRAM Architecture for Quantized CNNs using Fast Winograd Convolutions. . In International Symposium on Memory Systems (MEMSYS 2020). ACM/IEEE, 2020.

-

Efficient Generation of Application Specific Memory Controllers. . In International Symposium on Memory Systems (MEMSYS 2020). ACM/IEEE, 2020.

-

System Simulation with PULP Virtual Platform and SystemC. . In International Conference on High-Performance and Embedded Architectures and Compilers 2020 (HiPEAC), Workshop on: Rapid Simulation and Performance Evaluation: Methods and Tools (RAPIDO). 2020.

-

Fast and Accurate DRAM Simulation: Can we Further Accelerate it?. . In 2020 Design, Automation Test in Europe Conference Exhibition (DATE), pp. 364–369. 2020.

-

The gem5 Simulator: Version 20.0+. . 2020.

-

An Energy Efficient 3D-Heterogeneous Main Memory Architecture for Mobile Devices. . In International Symposium on Memory Systems (MEMSYS 2020). ACM/IEEE, 2020.

-

Moderne Speicherarchitekturen für leistungsfähige Infotainmentsysteme und autonomes Fahren. . In ATZelektronik, 15(11), pp. 16–21. 2020.

-

DRAMSys4.0: A Fast and Cycle-Accurate SystemC/TLM-Based DRAM Simulator. . In International Conference on Embedded Computer Systems Architectures Modeling and Simulation (SAMOS). Springer, 2020.

2019[ to top ]

-

A Lean, Low Power, Low Latency DRAM Memory Controller for Transprecision Computing. . In Embedded Computer Systems: Architectures, Modeling, and Simulation, D. N. Pnevmatikatos, M. Pelcat, M. Jung (eds.), pp. 429–441. Springer International Publishing, Cham, 2019.

-

Rapid Identification of Shared Memory in Multithreaded Embedded Systems with Static Scheduling. . In Proceedings of the 48th International Conference on Parallel Processing: Workshops, of ICPP 2019. Association for Computing Machinery, Kyoto, Japan, 2019.

-

3D Stacked DRAM Memories (Book chapter in the Handbook of 3D {I}ntegration). . Vol. 4. Wiley-VCH, 2019.

-

Fast Validation of DRAM Protocols with Timed Petri Nets. . In Proceedings of the International Symposium on Memory Systems, of MEMSYS ’19, pp. 133–147. ACM, Washington, District of Columbia, 2019.

-

NNDRAM: A Deep In-DRAM Computing Architecture for Neural Network Processing. . In IEEE International Symposium on Circuits and Systems (ISCAS). 2019.

-

RRAMSpec: A Design Space Exploration Framework for High Density Resistive RAM. . In 2019 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS). 2019.

-

Speculative Temporal Decoupling Using fork(). . In IEEE Conference on Design, Automation and Test in Europe (DATE), pp. 1721–1726. 2019.

2018[ to top ]

-

Enabling Continuous Software Engineering for Embedded Systems Architectures with Virtual Prototypes. . In Software Architecture, C. E. Cuesta, D. Garlan, J. Pérez (eds.), pp. 115–130. Springer International Publishing, Cham, 2018.

-

Efficient Coding Scheme for DDR4 Memory Subsystems. . In ACM International Symposium on Memory Systems (MEMSYS 2018). 2018.

-

The Role of Memories in Transprecision Computing. . In IEEE International Symposium on Circuits and Systems (ISCAS). 2018.

-

Driving Against the Memory Wall: The Role of Memory for Autonomous Driving. . In Workshop on New Platforms for Future Cars: Current and Emerging Trends at IEEE Conference Design, Automation and Test in Europe (DATE). 2018.

-

Improving the Error Behavior of DRAM by Exploiting its Z-Channel Property. . In IEEE Conference Design, Automation and Test in Europe (DATE). 2018.

-

Driving into the Memory Wall: The Role of Memory for Advanced Driver Assistance Systems and Autonomous Driving. . In Proceedings of the International Symposium on Memory Systems, of MEMSYS ’18, pp. 377–386. ACM, Alexandria, Virginia, 2018.

-

A Memory Centric Architecture of the Link Assessment Algorithm in Large Graphs. . In IEEE Design & Test, 35(1), pp. 7–15. 2018.

-

An Analysis on Retention Error Behavior and Power Consumption of Recent DDR4 DRAMs. . In IEEE Conference Design, Automation and Test in Europe (DATE). 2018.

-

A Model-Based Safety Analysis of Dependencies Across Abstraction Layers. . In Computer Safety, Reliability, and Security, B. Gallina, A. Skavhaug, F. Bitsch (eds.), pp. 73–87. Springer International Publishing, Cham, 2018.

-

BOSMI: A Framework for Non-intrusive Monitoring and Testing of Embedded Multithreaded Software on the Logical Level. . In Proceedings of the 18th International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation, of SAMOS ’18, pp. 131–138. ACM, Pythagorion, Greece, 2018.

-

A Framework for Non-Intrusive Trace-driven Simulation of Manycore Architectures with Dynamic Tracing Configuration. . In The 18th International Conference on Runtime Verification (RV 2018). 2018.

2017[ to top ]

-

DRAMSpec: A High-Level DRAM Timing, Power and Area Exploration Tool. . In International Journal of Parallel Programming, 45(6), pp. 1566–1591. 2017.

-

3D-Stacked Many-Core Architecture for Biological Sequence Analysis Problems. . In International Journal of Parallel Programming, pp. 1–41. 2017.

-

A Bank-Wise DRAM Power Model for System Simulations. . In Proceedings of the 9th Workshop on Rapid Simulation and Performance Evaluation: Methods and Tools, of RAPIDO ’17, pp. 5:1–5:7. ACM, Stockholm, Sweden, 2017.

-

System-Level Modeling, Analysis and Optimization of DRAM Memories and Controller Architectures. . University of Kaiserslautern, 2017.

-

System Simulation with gem5 and SystemC: The Keystone for Full Interoperability. . In 2017 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS), pp. 62–69. 2017.

-

Supervised Testing of Concurrent Software in Embedded Systems. . In 2017 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS), pp. 233–238. 2017.

-

A Platform to Analyze DDR3 DRAM’s Power and Retention Time. . In IEEE Design & Test, 34(4), pp. 52–59. 2017.

-

A New State Model for DRAMs Using Petri Nets. . In 2017 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS), pp. 221–226. 2017.

-

Integrating DRAM Power-Down Modes in gem5 and Quantifying their Impact. . In International Symposium on Memory Systems (MEMSYS17). 2017.

-

Using Run-Time Reverse-Engineering to Optimize DRAM Refresh. . In International Symposium on Memory Systems (MEMSYS17). 2017.

2016[ to top ]

-

Efficient Reliability Management in SoCs - An Approximate DRAM Perspective. . In 21st Asia and South Pacific Design Automation Conference (ASP-DAC). 2016.

-

Approximate Computing with Partially Unreliable Dynamic Random Access Memory - Approximate DRAM. . In Proceedings of the 53rd Annual Design Automation Conference, of DAC ’16, pp. 100:1–100:4. ACM, Austin, Texas, 2016.

-

A Customized Many-Core Hardware Acceleration Platform for Short Read Mapping Problems Using Distributed Memory Interface with 3D--Stacked Architecture. . In Journal of Signal Processing Systems, pp. 1–15. 2016.

-

Software Architectures for Embedded Software Systems. . Distance and Independent Studies Center (DISC) University of Kaiserslautern, 2016.

-

A New Bank Sensitive DRAMPower Model for Efficient Design Space Exploration. . In International Workshop on Power And Timing Modeling, Optimization and Simulation (PATMOS 2016). 2016.

-

Reverse Engineering of DRAMs: Row Hammer with Crosshair. . In International Symposium on Memory Systems (MEMSYS 2016). 2016.

-

A cross layer approach for efficient thermal management in 3D stacked SoCs. . In Microelectronics Reliability, 61, pp. 43–47. 2016.

-

Exploring System Performance using Elastic Traces: Fast, Accurate and Portable. . In IEEE International Conference on Embedded Computer Systems Architectures Modeling and Simulation (SAMOS), July, 2016, Samos Island, Greece. 2016.

-

ConGen: An Application Specific DRAM Memory Controller Generator. . In Proceedings of the Second International Symposium on Memory Systems, of MEMSYS ’16, pp. 257–267. ACM, Alexandria, VA, USA, 2016.

2015[ to top ]

-

Virtual Development on Mixed Abstraction Levels: an Agricultural Vehicle Case Study. . In Synopsys Usergroup Conference (SNUG). 2015.

-

DRAMSys: A flexible DRAM Subsystem Design Space Exploration Framework. . In IPSJ Transactions on System LSI Design Methodology (T-SLDM). 2015.

-

Thermal Aspects and High-level Explorations of 3D stacked DRAMs. . In IEEE Computer Society Annual Symposium on VLSI (ISVLSI). 2015.

-

A Custom Computing System for Finding Similarties in Complex Networks. . In Proceedings of the 2015 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), pp. 262–267. Montpellier, France, 2015.

-

Omitting Refresh - A Case Study for Commodity and Wide I/O DRAMs. . In 1st International Symposium on Memory Systems (MEMSYS 2015). Washington, DC, USA, 2015.

-

Coupling gem5 with SystemC TLM 2.0 Virtual Platforms. . In gem5 User Workshop, International Symposium on Computer Architecture (ISCA). Portland, OR, USA., 2015.

-

A High-Level DRAM Timing, Power and Area Exploration Tool. . In Embedded Computer Systems Architectures Modeling and Simulation (SAMOS). 2015.

-

Reliability and Thermal Challenges in 3D Integrated Embedded Systems. . In 1st International ESWEEK Workshop on Resiliency in Embedded Electronic Systems, Amsterdam, The Netherlands. 2015.

-

Retention Time Measurements and Modelling of Bit Error Rates of WIDE I/O DRAM in MPSoCs. . In Proceedings of the IEEE Conference on Design, Automation & Test in Europe (DATE). European Design and Automation Association, 2015.

2014[ to top ]

-

Thermal Modelling of 3D Stacked DRAM with Virtual Platforms. . In Tenth International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES14), Vol. 10. Academia Press, Ghent, Belgium, 2014.

-

Energy Optimization in 3D MPSoCs with Wide-I/O DRAM Using Temperature Variation Aware Bank-Wise Refresh. . In Design, Automation and Test in Europe Conference and Exhibition (DATE), 2014, pp. 1–4. 2014.

-

Optimized active and power-down mode refresh control in 3D-DRAMs. . In Very Large Scale Integration (VLSI-SoC), 2014 22nd International Conference on, pp. 1–6. 2014.

2013[ to top ]

-

Virtual Platforms for Fast Exploration of Computing Systems in Finance. . In Young Researcher Symposium, YRS 2013. Proceedings, pp. 18–23. Fraunhofer Verlag, 2013.

-

Virtual Platforms for Fast Memory Subsystem Exploration Using gem5 and TLM2.0. . In Ninth International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES13), Vol. 9, pp. 153–156. Academia Press, Ghent, Belgium, 2013.

-

Power Modelling of 3D-Stacked Memories with TLM2.0 based Virtual Platforms. . In Synopsys User Group Conference (SNUG), May, 2013, Munich, Germany. 2013.

-

TLM modelling of 3D stacked wide I/O DRAM subsystems: a virtual platform for memory controller design space exploration. . In Proceedings of the 2013 Workshop on Rapid Simulation and Performance Evaluation: Methods and Tools, of RAPIDO ’13, pp. 5:1–5:6. ACM, Berlin, Germany, 2013.

2012[ to top ]

-

A Scalable Multi-Core ASIP Virtual Platform For Standard-Compliant Trellis Decoding. . In Synopsys User Group Conference (SNUG). Munich, Germany, 2012.

2011[ to top ]

-

Energy Efficient Acceleration and Evaluation of Financial Computations towards Real-Time Pricing. . In Knowledge-Based and Intelligent Information and Engineering Systems, Vol. 6884, A. König, A. Dengel, K. Hinkelmann, K. Kise, R. J. Howlett, L. C. Jain (eds.), pp. 177–186. Springer Berlin Heidelberg, Heidelberg, 2011.