Completed Theses

2026

Design and Exploration of Configurable GPU Architectures through System-Level Simulation

Type:

Bachelor Thesis

Student:

Henrick Bonda

Date:

20th of January 2026

Summary:

Today, Graphics Processing Units (GPUs) are not just used graphics but also often employed for more general-purpose tasks like machine learning and scientific computing, driving the need for complex, configurable architectures. This thesis introduces a system-level simulation framework combining the gem5 and DRAMSys simulators to model and evaluate the AMD MI300X GPU, ensuring compatibility and enabling experiments with various workloads—including matrix operations. By evaluating the influence of, i.a., GPU frequency and the number of Compute Units, an insight into key design parameters is provided. These findings provide a foundation for simulating and optimizing future GPU architectures.

2025

Evaluating Hardware Implementations for DRAM Address Mapping

Type:

Bachelor Thesis

Student:

Ludwig Friedl

Date:

10th of December 2025

Summary:

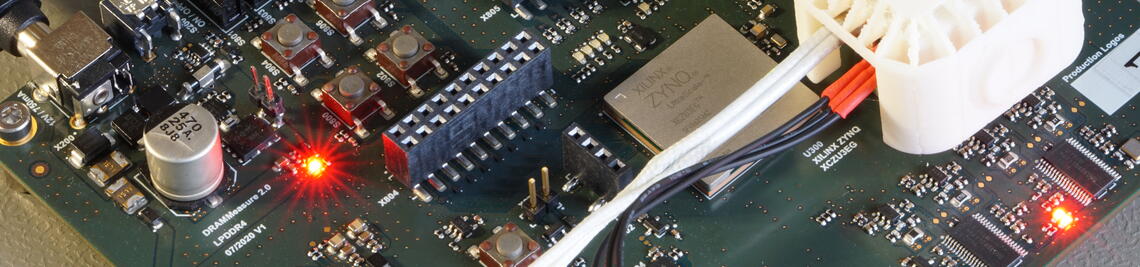

The "memory wall" gap between processor speed and memory bandwidth makes it crucial for memory-intensive applications to maximize bandwidth usage, where address mapping plays a key role. While hardwired mappings require fixed access patterns, reconfigurable implementations allow dynamic adjustments but add hardware overhead and initial delay. To evaluate trade-offs, two Verilog address mappings for FPGAs were implemented and synthesized, and then integrated into the DRAMSys simulator to compare performance: a general-purpose mapping versus an optimized one with added delay. Furthermore, mappings that reserve memory areas for metadata, such as error correction codes, to improve system reliability were also explored.

RoRiV: Porting the Real-Time Operating System RODOS on RISC-V

Type:

Bachelor Thesis

Student:

Andreas Theiner

Date:

27th of September 2025

Summary:

In this thesis, a port of the Real-Time Operating System RODOS on a RISC-V CPU is developed. For this purpose, the PicoSoC, which is a System-on-a-Chip with a PicoRV32 core, is employed on the pico-ice and Basys3 boards. RODOS provides three benchmarks that give a rough estimate of the performance. These benchmarks of various versions of the PicoSoC combined with different hardware are evaluated and compared to the results of already existing ports. The comparison shows, that the time taken for a thread yield of this port (Basys3: 394μs) is significantly longer than other comparable ports need (SF2 M2S060: 30μs) but still short in absolute terms. The explanation of this difference requires further research. Since the PicoRV32 does not fully comply with the RISC-V ISA, this port requires few changes to work with other boards. But it lays the groundwork for running RODOS on a RISC-V board.

PIM-Bridge: Operating System Framework for Processing-in-Memory DRAM

Type:

Bachelor Thesis

Student:

Tom Köstler

Date:

8th of September 2025

Summary:

As machine learning and large language models (LLMs) grow rapidly, so does their demand for data and computation. Deep neural networks (DNNs) require massive data and are typically trained on accelerators like TPUs. Increasingly, system performance is limited not by compute power but by DRAM memory bandwidth. Processing-in-Memory (PIM) architectures address this by embedding computation within memory, reducing data transfer bottlenecks. This thesis presents PIM-Bridge, an operating system framework for Processing-in-Memory DRAM that enables the use of one of the first real-world PIM implementations called PIM-HBM of the memory manufacturer Samsung. PIM-Bridge consists of a character device driver for PIM-functionality as well as utility infrastructure. It is evaluated using the gem5 architecture simulator and the DRAMSys memory model.

Effects of Overclocking Profiles on the Performance of DRAM

Type:

Bachelor Thesis

Student:

Gerner Marcus

Date:

11th of April 2025

Summary:

DRAM is widely used in our technological world. There are different generations and variations of DRAM like DDR4 or DDR5. And in every generation or variation there are different manufacturers of DRAM devices like Samsung or Hynix, which build these devices in different steppings like A-Die or M-Die by Hynix for DDR5. Every of these devices have different capabilities in enhancing the performance relevant data rate and timings. To look for specialized overclockable DRAM devices can give the possibility to increase the performance by far because a lot of minimum required JEDEC specified timings can be enhanced depending on the used DRAM devices. Two of these devices, one for DDR4 and one for DDR5, are used for this thesis to overclock the timings and data rate. It delivers results up to 46 % higher performance for DDR4, respectively up to 37 % more performance for DDR5. Furthermore, two real-world environments, the AM4 as well as the AM5 platform, are compared with the DRAM simulator DRAMSys4.0 to show differences and equality between them.

Development of a GPS-DO for a Satellite Ground-Station

Type:

Bachelor Thesis

Student:

Moritz Gellermann

Date:

28th of February 2025

Summary:

In this thesis a Global Positioning System (GPS) based frequency standard is developed and build. The comparison with a commercial frequency standard shows a sufficient accuracy for the intended use in an amateur radio ground-station.

2024

Extension of a RISC-V Core for Discrete Event Simulation Acceleration

Type:

Bachelor Thesis

Student:

Timo Grundheber

Date:

17th of November 2024

Summary:

This thesis explores integrating a hardware accelerator into a Discrete Event Simulation (DES) framework, focusing on its impact on simulation performance. A custom project using the PicoRV32 processor was developed, including a discrete event simulator in C++ and an accelerator with priority and process queues. The results showed a 1.3-2.3x speedup in execution time, particularly benefiting event-dominated simulations, highlighting the importance of hardware accelerators in modern System on Chip designs and DES.

Measuring End-to-End Latency in Applications with an FPGA

Type:

Bachelor Thesis

Student:

Yannik Stamm

Date:

20th of October 2024

Summary:

This thesis is concerned with the development of a prototype for external and online latency measurement. The concept builds upon the use of an FPGA board and measures end-to-end latency by sniffing input signals directly from input devices, encoding the inputs into the video signal, and reading the encoded inputs again. This concept is implemented with the "Snickerdoodle Black" and the "piSmasher" boards and a mouse as input device. The prototype does work with further potential being promising.

Development of an Automated Recognition of QSL Cards

Type:

Bachelor Thesis

Student:

Fabian Schmitt

Date:

6th of September 2024

Summary:

Amateur radio enables radio conversations between radio amateurs worldwide, who traditionally confirm each other with QSL cards. These cards contain the sender's and recipient's call signs and are distributed by national associations. In Germany, a sorting machine with manual assistance is used. This work aimed at improving the system with Optical Character Recognition (OCR) to automatically recognize call signs and increase the efficiency of card distribution was achieved through an improved OCR system and preprocessing.