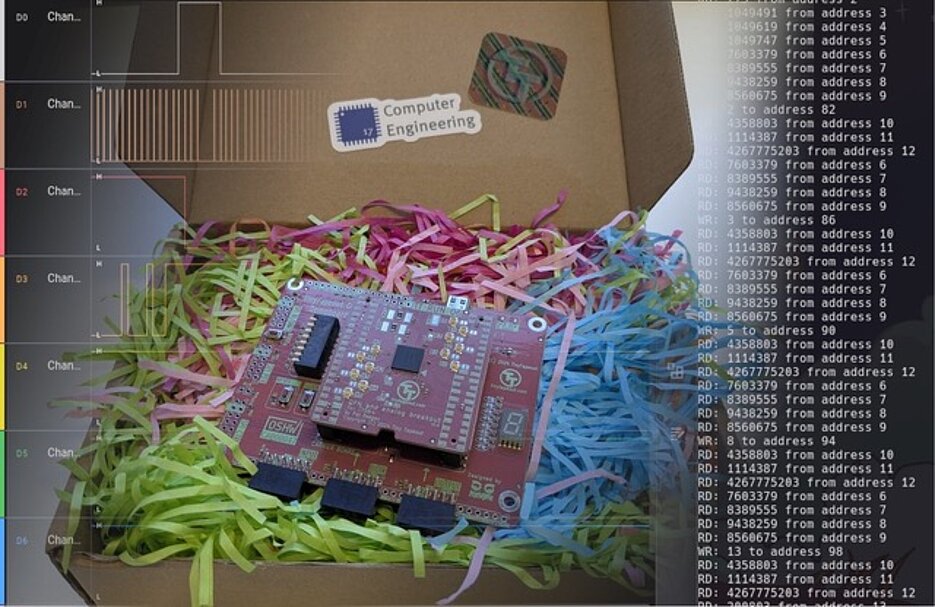

Second chip of the CE Group manufactured

02/03/2025The Computer Engineering group has developed its second low-cost chip with a 32-bit RISC-V CPU to provide students with hands-on experience in chip design.

The chip features a compact 32-bit RISC-V CPU based on the reduced TinyRV1 instruction set from Cornell University, which is already successfully used in teaching at JMU. It was developed using 130 nm technology, targeting a clock speed of 12 MHz. Initial tests confirm the functionality of the design. Due to its simplicity, this chip is ideal for use in future courses, as it provides a practical connection between lecture theory and chip design. In the context of the Embedded Processor Lab and theses, students can design and produce their own chips. A third design has already been submitted for tape-out and is currently in production. Additional designs are planned for future iterations of Tiny Tapeout.